Highly-parallel Two-dimensional Cellular Automaton Architecture and its Application to Real-time Image Processing

Takeshi Ikenaga

March 2001

## Summary

The focus of this dissertation is the design of a highly-parallel computer for real-time image-understanding processing, one that is extremely compact and provides very high levels of performance. This computer can be used for implementation of various imageunderstanding applications in the fields of industrial inspection, medical imaging, intelligent transportation systems (ITS), robotics, multimedia, human interface, entertainment, image coding, and so forth.

The result is CAM<sup>2</sup>, which stands for Cellular AutoMata on Content-Addressable Memory. As the name shows, this new architecture combines cellular automaton (CA) and content-addressable memory (CAM). A CA is a promising computer paradigm that can break through the von Neumann bottleneck. A two-dimensional CA is especially suitable for application to pixel-level image processing because an image has a two-dimensional topology. Although various architectures for processing two-dimensional CA have been proposed, there are no compact, practical computers. So, in spite of its great potential, CA is not widely used. To remedy this situation, I can think of a CAM turned to CA processing. CAM, or an associative processor, that can perform various types of parallel processing with words as the basic unit is a promising component for creating a compact CA cell array because of its suitability for LSI implementation. CAM makes it possible to embed an enormous number of processing elements (PEs), corresponding to CA cells, in one VLSI chip. It can attain pixel-order parallelism on a single board.

There are three basic problem areas that must be integrated in order to produce a high-performance, compact, and flexible  $CAM^2$  and demonstrate its usefulness for real-time image-understanding processing. These three areas are

- 1. computer architecture,

- 2. LSI and system design and implementation, and

- 3. applications.

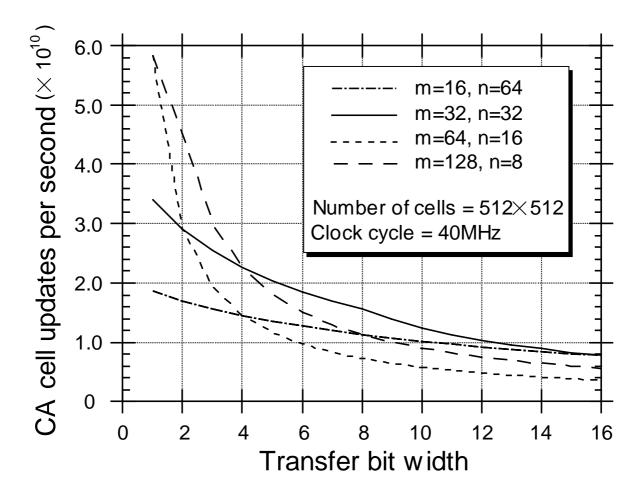

In the computer architecture area, the study effort is focused on the following three architectural considerations: CA mapping, CA processing, and data loading and retrieval processing. Multiple-zigzag mapping enables two-dimensional CA cells to be mapped into CAM words, even though physically a CAM has a one-dimensional structure. Dedicated CAM functions enable high-performance CA processing. Furthermore, parallel loading and partial word retrieval techniques enable high-throughput data transfer between  $CAM^2$ and the outside image buffer. The performance evaluation results show that 256 k CA cells, which correspond to a 512 × 512 pixel picture, can be processed by a  $CAM^2$  on a single board using deep sub-micron process technology. Moreover, the processing speed is more than 10 billion CA cell updates per second (CUPS). This means that more than a thousand CA-based image processing operations can be performed on a 512 × 512 pixel image at video rates (33 msec). These results demonstrate that  $CAM^2$  will represent a major step toward the development of a compact and high-performance two-dimensional cellular automaton.

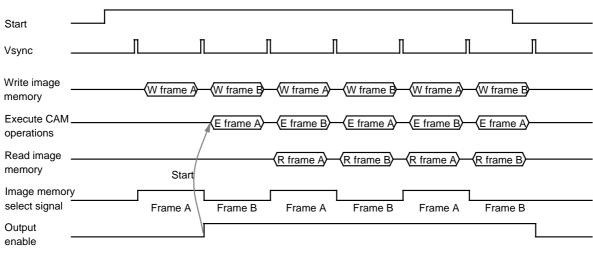

In the design and implementation area, fully-parallel 1-Mb CAM LSIs with dedicated functions for CA processing have been designed and fabricated, as has a proof-of-concept prototype CAM<sup>2</sup> system (PC board) using these LSIs. To satisfy the extremely severe design constraints of the state-of-the-art process technology (0.25  $\mu$ m), this study involves not only VLSI circuit design, but also packaging technology, circuit board fabrication technology, power and signal distribution techniques, heat dissipation problems and design and verification strategy. The CAM chip capable of operating at 56 MHz with 2.5-V power supply was fabricated using 0.25- $\mu$ m full-custom CMOS technology with five aluminum layers. A total of 15.5 million transistors have been integrated into a 16.1×17.0-mm chip. Typical power dissipation is 0.25 W. The processing of various update and data transfer operations was performed at 3-640 GOPS. The fabricated CAM has 16 k words, or processing elements (PEs), which can process  $128 \times 128$  pixels in parallel, and a board-sized pixel-parallel image processing system can be implemented using several chips. Indeed, the prototype board has a two-dimensional array (2 × 2) of CAM chips, and can handle a 256 × 256 pixel image. Since PCI bus and NTSC video interfaces are also embedded in the board, a compact image-processing platform can be built simply by connecting the board to a personal computer and a video camera. The LSI and the board confirm that an economically feasible, compact, high-performance, and flexible CAM<sup>2</sup> can be actually obtained with the current technology.

In the application area, two rather advanced computation paradigms based on CA are taken up: discrete-time cellular neural network (DTCNN) and mathematical morphology. DTCNN is a promising computer paradigm that fuses artificial neural networks (ANN) with the concept of CA. Mathematical morphology is an image transformation technique that locally modifies geometric features through set operations. Both are becoming powerful tools with various applications in image processing field. Here, efficient mapping and processing methods to perform various kinds of DTCNN and morphology processing are studied. Evaluation results show that, on average,  $CAM^2$  can perform one transition for various DTCNN templates in about 12  $\mu$ sec. CAM<sup>2</sup> also can perform one morphological operation for basic structuring elements within 30  $\mu$ sec. These results mean that more than a thousand operations can be carried out on an entire  $512 \times 512$  pixel image at video rates (33 msec). Furthermore,  $CAM^2$  can perform practical image processing through a combination of DTCNN, morphology, and other algorithms. These results demonstrate that  $CAM^2$  will enable fuller realization of the potential of DTCNN and morphology and contribute significantly to the development of real-time image processing systems based on DTCNN, morphology and a combination of them.

## Acknowledgements

First and foremost, I express my sincere appreciation to Professor Katsuhiko Shirai of Waseda University for his encouragement, constant guidance, and support during the writing of this dissertation. I also express my gratitude to Professor Yoichi Muraoka, Professor Masao Yanagisawa and Professor Hayato Yamana of Waseda University for reviewing this work. I also thank Professor Shigeki Goto and the other faculty members at Information & Computer Science Department of Waseda University for their insightful comments at the public hearing.

The research reported in this dissertation was conducted from 1996 to 1999 in NTT LSI Laboratories, NTT System Electronics Laboratories, NTT Integrated Information & Energy Systems Laboratories and NTT Lifestyle and Environmental Technology Laboratories. I express my deep thanks to Mr. Yasuyoshi Sakai (Advanced Telecommunications Research Institute International (ATR)), Mr. Masataka Hirai (NTT AFTY Co.) Dr. Ken-ichi Nakano (NTT Advanced Technology Co.), Dr. Ichiro Yamada (NTT Lifestyle and Environmental Technology Labs.), Dr. Osamu Karatsu (SRI consulting K. K.), Mr. Ken Takeya (NTT Telecommunications Energy Labs.), Dr. Ryota Kasai (NTT Electronics Co.), Dr. Shoji Makino (NTT Communication Science Labs.), and Dr. Hitoshi Kitazawa (NTT Lifestyle and Environmental Technology Labs.) for their administrative support and encouragement.

I express my sincere thanks to my two mentors on CAM-based computer vision hardware: Dr. Takeshi Ogura (NTT Lifestyle and Environmental Technology Labs.) and Professor Charles C. Weems (University of Massachusetts, Amherst) for their direct guidance, criticism, helpful suggestions, and continuous encouragement during the research. I also thank Professor Hironori Yamauchi (Ritsumeikan University) and Dr. Jun-ichi Takahashi (Deloitte Tohmatsu Consulting) for giving me the opportunity to start research in the LSI and computer architecture fields and for their guidance.

Furthermore, I thank Professor Toshio Kondo (Mie University), Professor Shinji Yamamoto (Toyohasi University of technology), Professor Keikichi Tamaru, Professor Hidetoshi Onodera, Dr. Kazutoshi Kobayashi (Kyoto University), Dr. Katsunori Shimohara, Mr. Hitoshi Henmi (Advanced Telecommunications Research Institute International (ATR)), Mr. Kuniharu Uchimura, Mr. Hisao Nojima, Mr. Mamoru Nakanishi, Ms. Namiko Ikeda, Ms. Miki Kitabata (NTT Lifestyle and Environmental Technology Labs.), Mr. Kimihisa Aihara (NTT Science and Core Technology Laboratory Group), Mr. Yuichi Fujino, Mr. Tadashi Nakanishi (NTT Cyber Solutions Labs.), Mr. Makoto Endo, Dr. Jiro Naganuma, Mr. Takeshi Yoshitome, Mr. Yutaka Tashiro, Mr. Hiroaki Matsuda, Mr. Koyo Nitta, Dr. Sakuichi Otsuka, Ms. Yasuko Takahashi (NTT Cyber Space Labs.), Mr. Junji Yamato (NTT Communication Science Labs.), Dr. Toshiaki Miyazaki, Dr. Shin-ichi Minato, Mr. Tsunemasa Hayashi(NTT Network Innovation Labs.), Mr. Tomoji Toriyama, Dr. Masahito Kawamori (NTT Service Integration Labs.), Mr. Osamu Saito (NTT Information Sharing Platform Labs.), Mr. Toshihiro Minami (NTT Intellectual Property Center), Mr. Ritsu Kusaba, Mr. Eiichi Hosoya (NTT Communications Co.), Mr. Tetsuya Abe, Mr. Kazuhito Suguri (NTT East), Mr. Tsuneo Okubo, Mr. Toshio Tsuchiya and Mr. Mitsuo Ikeda (NTT Electronics Co.) for their technical support and fruitful discussions, and Mr. Tatsuo Baba and Mr. Yasuharu Nakabayashi (NTT Electronics Co.) for contributions to the development of the CAM LSI.

Finally, I thank my parents, my wife, and my daughter and son for their kind support over the years.

## Contents

| 1        | Intr | oducti  | on                                                                                                 | 1  |

|----------|------|---------|----------------------------------------------------------------------------------------------------|----|

|          | 1.1  | Backg   | round and purpose of this dissertation                                                             | 1  |

|          |      | 1.1.1   | Cellular automaton as a computation paradigm for image processing                                  | 1  |

|          |      | 1.1.2   | Architecture for 2D cellular automata                                                              | 3  |

|          | 1.2  | Key te  | echnologies: HiPIC and CAM                                                                         | 6  |

|          |      | 1.2.1   | System model for image processing                                                                  | 6  |

|          |      | 1.2.2   | LSI architecture for CA cell array                                                                 | 8  |

|          | 1.3  | Thesis  | scope                                                                                              | 11 |

| <b>2</b> | Cell | lular a | utomaton architecture: CAM <sup>2</sup>                                                            | 15 |

|          | 2.1  | Introd  | uction $\ldots$   | 15 |

|          | 2.2  | Basic : | architecture                                                                                       | 16 |

|          |      | 2.2.1   | $CAM^2$ based on HiPIC                                                                             | 16 |

|          |      | 2.2.2   | Dedicated CAM features for $CAM^2$                                                                 | 18 |

|          |      | 2.2.3   | Highly-parallel PE array with multiple-zigzag mapping                                              | 21 |

|          | 2.3  | CA pr   | ocessing $\ldots$ | 24 |

|          |      | 2.3.1   | CA-value transfer                                                                                  | 25 |

|          |      | 2.3.2   | CA-value update                                                                                    | 28 |

|          | 2.4  | Data l  | oading and retrieval processing                                                                    | 32 |

|          |      | 2.4.1   | Parallel loading                                                                                   | 32 |

|          |      | 2.4.2   | Partial retrieval                                                                                  | 36 |

|          | 2.5  | Evalua  | ation                                                                                              | 38 |

| 2.6<br><b>1-M</b><br>3.1<br>3.2 | [ <b>b CA</b> ]<br>Introd                                                                       | Processing performance evaluations                                                                                                                                                                                                        | 45<br><b>47</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------------------------------|-------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>1-</b> M<br>3.1              | Ib CA<br>Introd<br>CAM<br>3.2.1                                                                 | M LSI and CAM <sup>2</sup> board<br>luction                                                                                                                                                                                               | <b>47</b><br>47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 3.1                             | Introd<br>CAM<br>3.2.1                                                                          | luction                                                                                                                                                                                                                                   | 47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                 | CAM<br>3.2.1                                                                                    | LSI design                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 3.2                             | 3.2.1                                                                                           |                                                                                                                                                                                                                                           | 49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                 |                                                                                                 | Chip level design                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                 | 3.2.2                                                                                           |                                                                                                                                                                                                                                           | 49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                 |                                                                                                 | CAM block and cell circuit level design                                                                                                                                                                                                   | 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                 | 3.2.3                                                                                           | Data and clock distribution                                                                                                                                                                                                               | 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 3.3                             | Instru                                                                                          | ction design                                                                                                                                                                                                                              | 56                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                 | 3.3.1                                                                                           | Data transfer and update operations                                                                                                                                                                                                       | 56                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                 | 3.3.2                                                                                           | Multi-bit arithmetic operations                                                                                                                                                                                                           | 58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                 | 3.3.3                                                                                           | Global data operations                                                                                                                                                                                                                    | 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                 | 3.3.4                                                                                           | Instruction set                                                                                                                                                                                                                           | 60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 3.4                             | Design                                                                                          | a and verification procedure                                                                                                                                                                                                              | 61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 3.5                             | Fabric                                                                                          | ated LSI and its specifications                                                                                                                                                                                                           | 63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 3.6                             | A pro-                                                                                          | of-of-concept prototype $CAM^2$ board $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                                                                                                               | 66                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 3.7                             | Concl                                                                                           | usion                                                                                                                                                                                                                                     | 72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| App                             | olicatio                                                                                        | on: Discrete-time CNN                                                                                                                                                                                                                     | 75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 4.1                             | Introd                                                                                          | luction                                                                                                                                                                                                                                   | 75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 4.2                             | Defini                                                                                          | tion of DTCNN                                                                                                                                                                                                                             | 76                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 4.3                             | DTCN                                                                                            | NN Processing using $CAM^2$                                                                                                                                                                                                               | 79                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                 | 4.3.1                                                                                           | Keys to DTCNN mapping                                                                                                                                                                                                                     | 79                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                 | 4.3.2                                                                                           | DTCNN mapping                                                                                                                                                                                                                             | 79                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                 | 4.3.3                                                                                           | DTCNN processing procedure                                                                                                                                                                                                                | 85                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

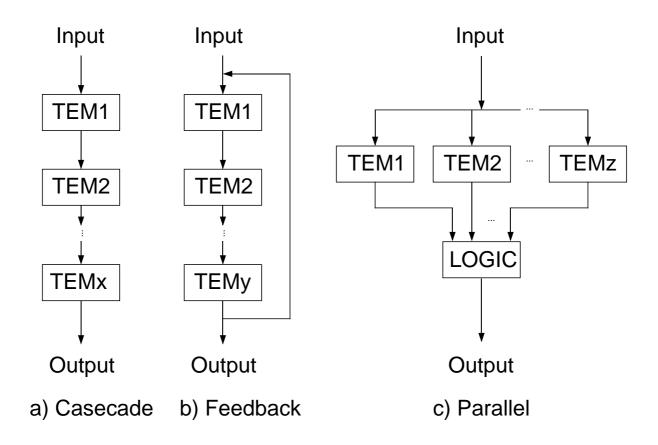

|                                 | 4.3.4                                                                                           | Multiple-layer DTCNN processing                                                                                                                                                                                                           | 86                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                 |                                                                                                 |                                                                                                                                                                                                                                           | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                 | <ul> <li>3.5</li> <li>3.6</li> <li>3.7</li> <li><b>App</b></li> <li>4.1</li> <li>4.2</li> </ul> | 3.3.3         3.3.4         3.4         3.4         3.5         Fabric         3.6       A prod         3.7       Conclu         4.1       Introd         4.2       Defini         4.3       DTCN         4.3.1       4.3.2         4.3.3 | 3.3.3 Global data operations         3.3.4 Instruction set         3.3.4 Instruction set         3.4 Design and verification procedure         3.5 Fabricated LSI and its specifications         3.6 A proof-of-concept prototype CAM <sup>2</sup> board         3.7 Conclusion         Application: Discrete-time CNN         4.1 Introduction         4.2 Definition of DTCNN         4.3 DTCNN Processing using CAM <sup>2</sup> 4.3.1 Keys to DTCNN mapping         4.3.2 DTCNN mapping         4.3.3 DTCNN processing procedure |

|          | 4.5 | Evalua   | tion $\ldots$        | 91  |

|----------|-----|----------|-------------------------------------------------------------------------------------------------------|-----|

|          |     | 4.5.1    | Processing performance                                                                                | 91  |

|          |     | 4.5.2    | Image processing                                                                                      | 91  |

|          | 4.6 | Conclu   | $\operatorname{sion}$                                                                                 | 96  |

| <b>5</b> | Арр | plicatio | n: mathematical morphology                                                                            | 99  |

|          | 5.1 | Introdu  | action                                                                                                | 99  |

|          | 5.2 | Definit  | ion of morphology                                                                                     | 101 |

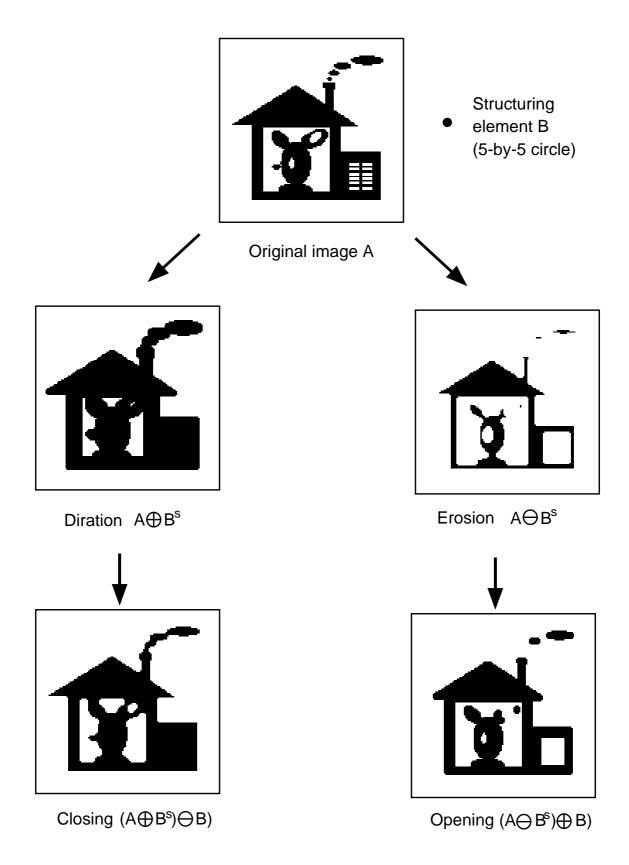

|          |     | 5.2.1    | Dilation and erosion                                                                                  | 101 |

|          |     | 5.2.2    | Opening and closing                                                                                   | 102 |

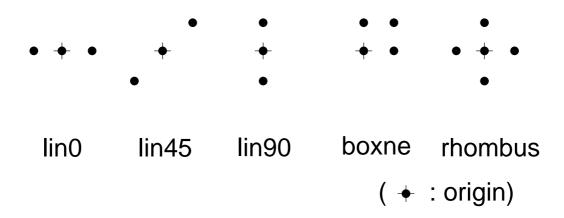

|          | 5.3 | Morph    | ology processing using $CAM^2$                                                                        | 103 |

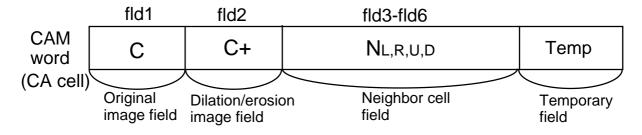

|          |     | 5.3.1    | Features of $CAM^2$ functions $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 103 |

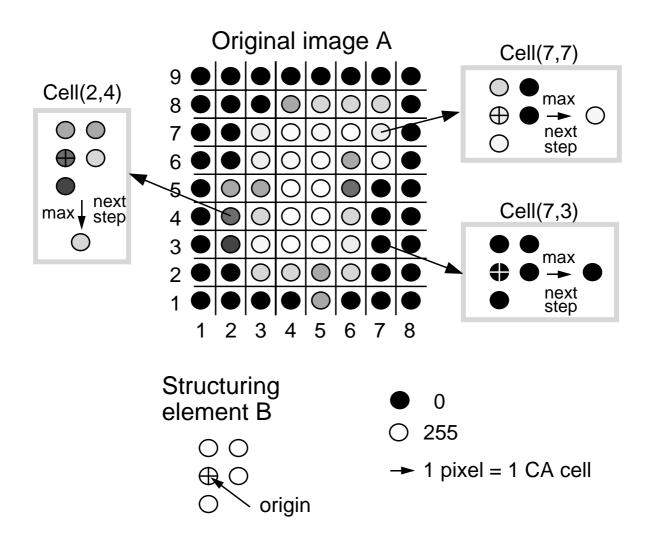

|          |     | 5.3.2    | Morphology mapping to $CAM^2$                                                                         | 105 |

|          |     | 5.3.3    | Morphology processing method                                                                          | 105 |

|          |     | 5.3.4    | Processing method for large and complex SEs                                                           | 109 |

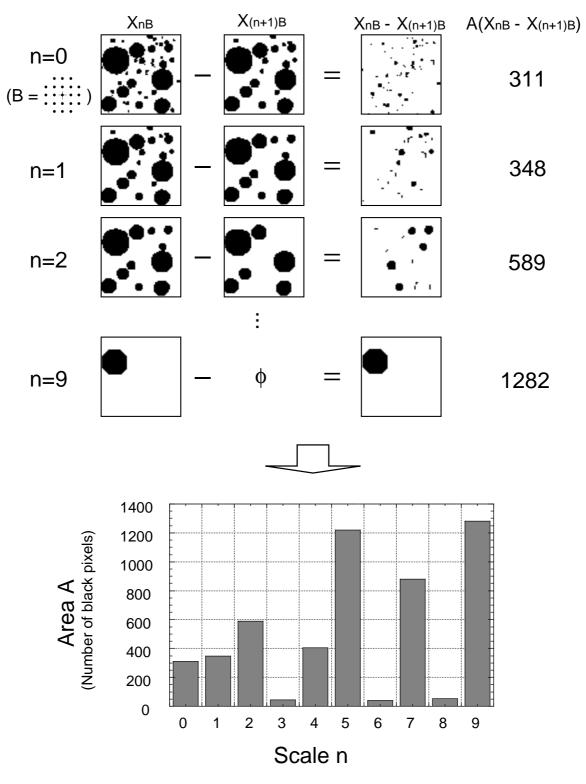

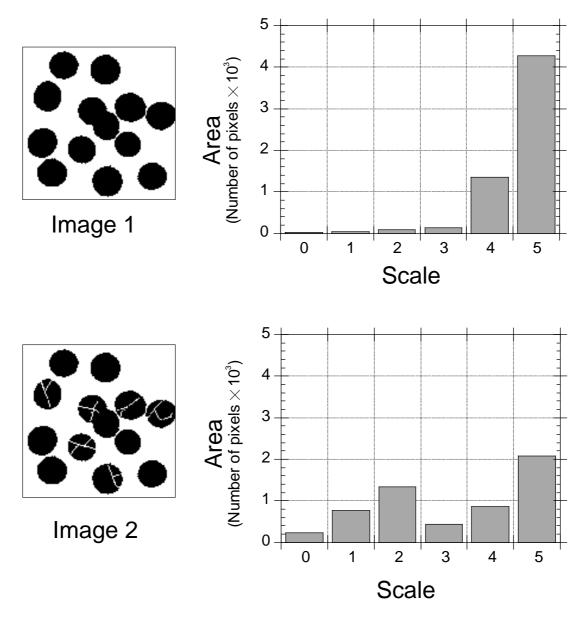

|          | 5.4 | Patterr  | n spectrum processing                                                                                 | 110 |

|          |     | 5.4.1    | Pixel-by-pixel subtraction                                                                            | 110 |

|          |     | 5.4.2    | Area calculation                                                                                      | 112 |

|          |     | 5.4.3    | Null set assessment                                                                                   | 113 |

|          | 5.5 | Evalua   | tion $\ldots$        | 114 |

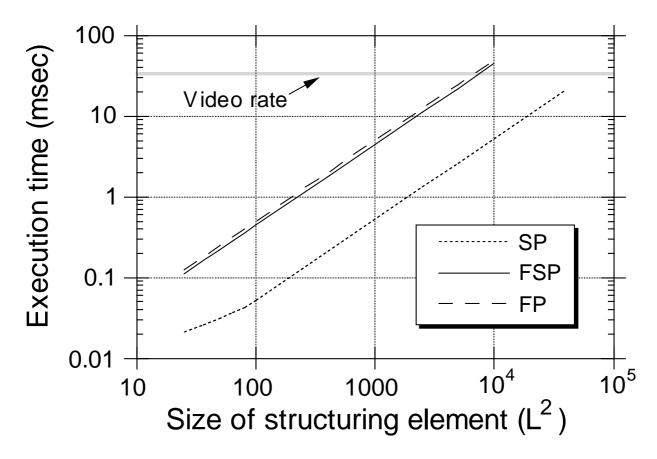

|          |     | 5.5.1    | Processing performance                                                                                | 114 |

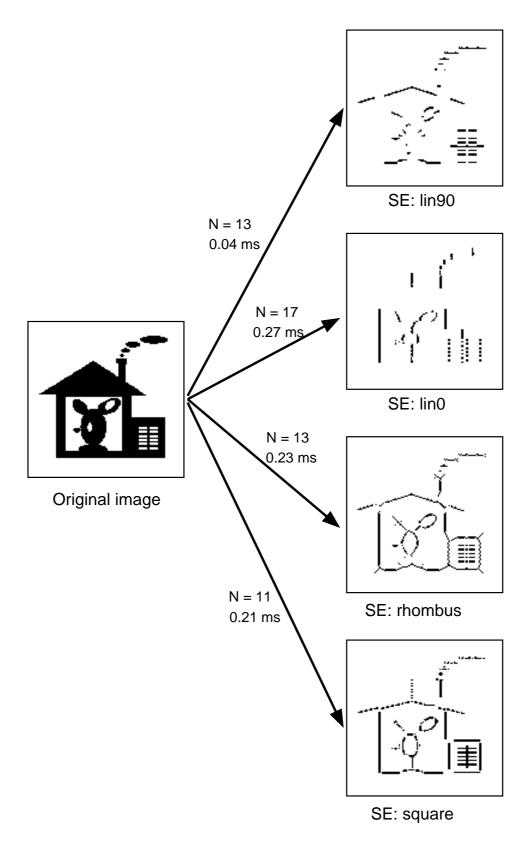

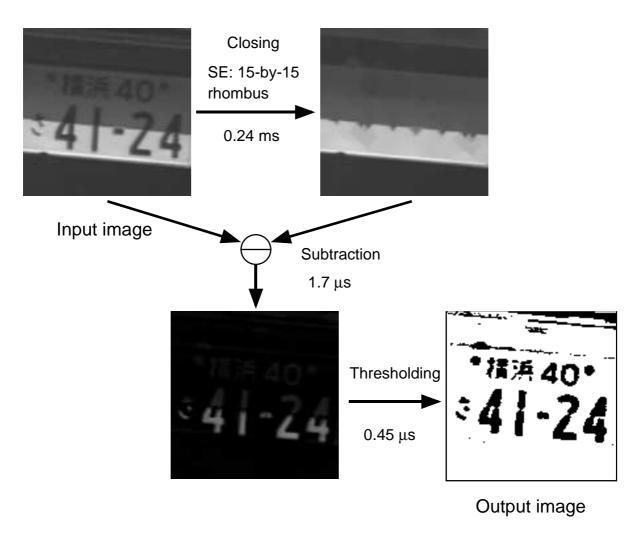

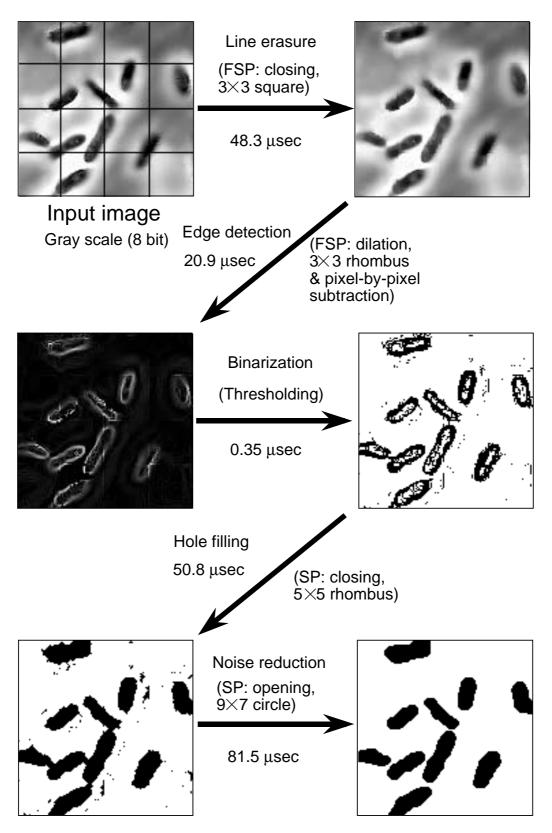

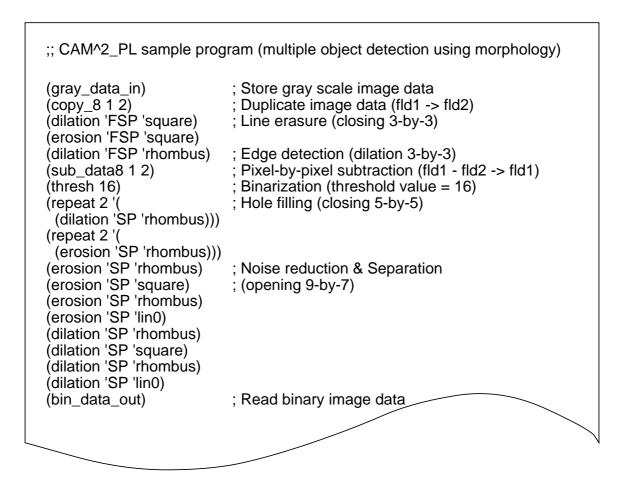

|          |     | 5.5.2    | Image processing                                                                                      | 115 |

|          | 5.6 | Conclu   | $\operatorname{sion}$                                                                                 | 125 |

| 6        | Con | nclusion | ı                                                                                                     | 127 |

|          | 6.1 | Summa    | ary of results                                                                                        | 127 |

|          | 6.2 | Future   | work                                                                                                  | 129 |

|          |     | 6.2.1    | Off-chip high-speed memory                                                                            | 129 |

|          |     | 6.2.2    | Multilevel vision architecture                                                                        | 130 |

| 6.2.3 Humanoid computer with multi-modal man-machine interface | 132 |

|----------------------------------------------------------------|-----|

| Bibliography                                                   | 135 |

| Author Biography                                               | 145 |

| Publication List                                               | 147 |

# List of Figures

| 1.1  | Model of two-dimensional cellular automaton.                                | 2  |

|------|-----------------------------------------------------------------------------|----|

| 1.2  | Basic idea of HiPIC.                                                        | 7  |

| 1.3  | Image processing systems on HiPIC.                                          | 7  |

| 1.4  | CAM development trend                                                       | 10 |

| 1.5  | Organization of this dissertation.                                          | 14 |

| 2.1  | Features of $CAM^2$ on HiPIC                                                | 17 |

| 2.2  | Block diagram of the dedicated CAM                                          | 20 |

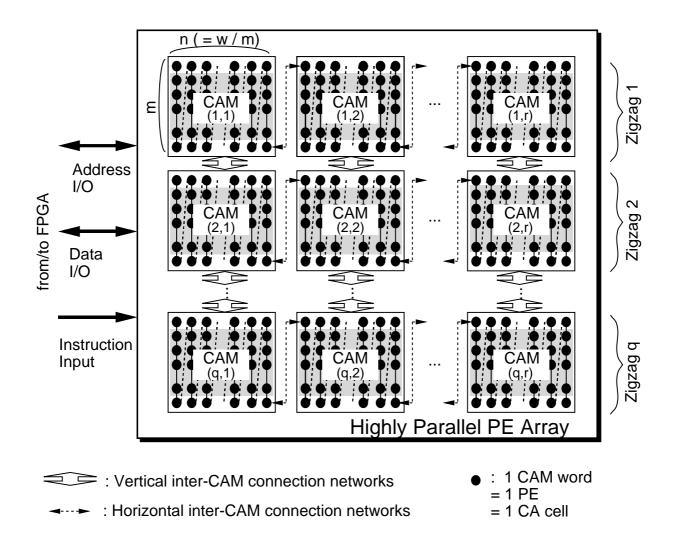

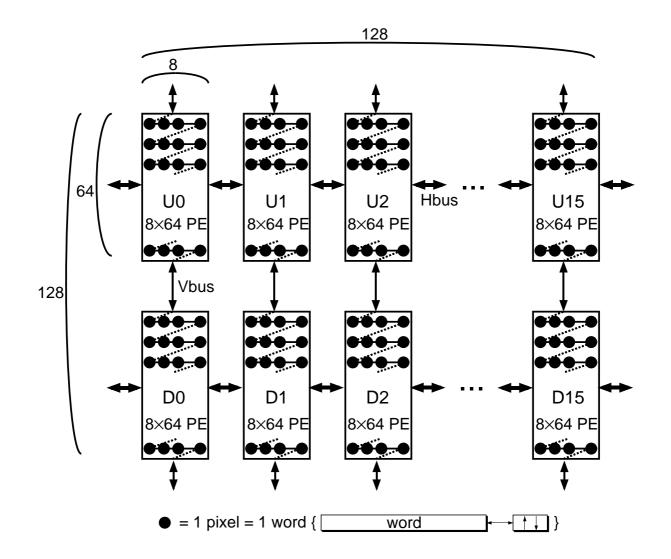

| 2.3  | Configuration of the highly-parallel PE array.                              | 22 |

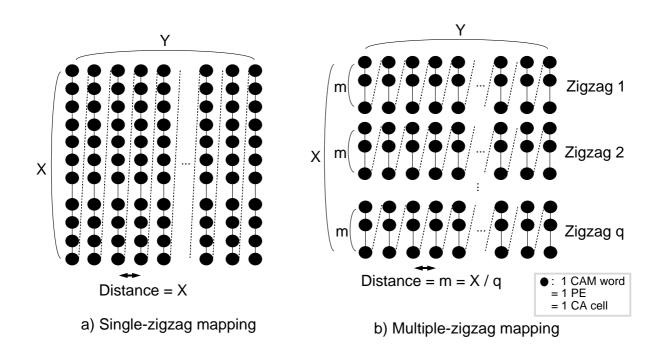

| 2.4  | Comparison of single and multiple zigzag mapping                            | 23 |

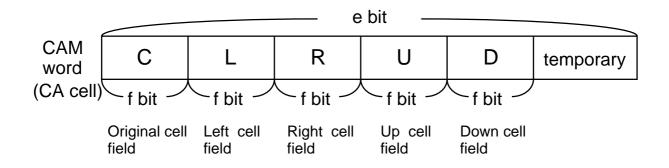

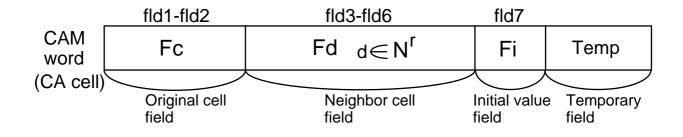

| 2.5  | CAM word configuration for a four-neighbor CA model                         | 24 |

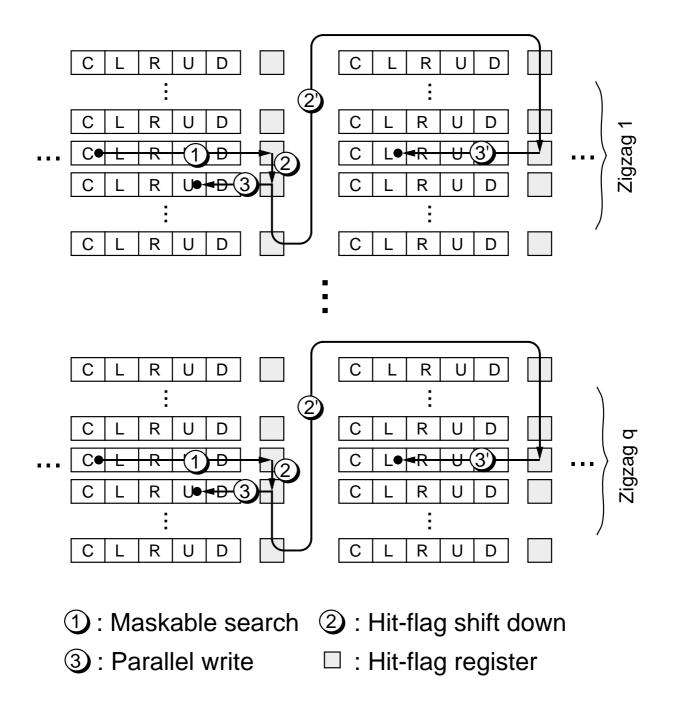

| 2.6  | Example of intra-CAM transfer (1 bit, to the right and down CA cells)       | 27 |

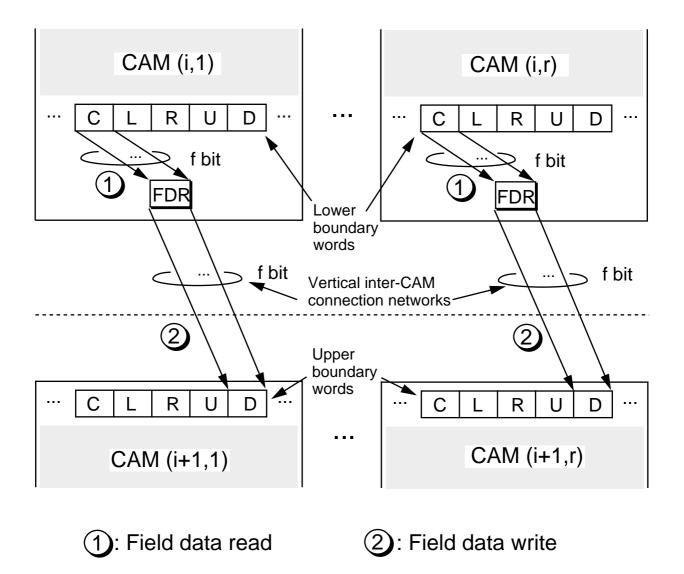

| 2.7  | Example of inter-CAM transfer ( $f$ bit, from lower boundary words to upper |    |

|      | boundary words.                                                             | 29 |

| 2.8  | Example of greater than operation $\{greater\_than(X,Y) \Rightarrow X\}$    | 31 |

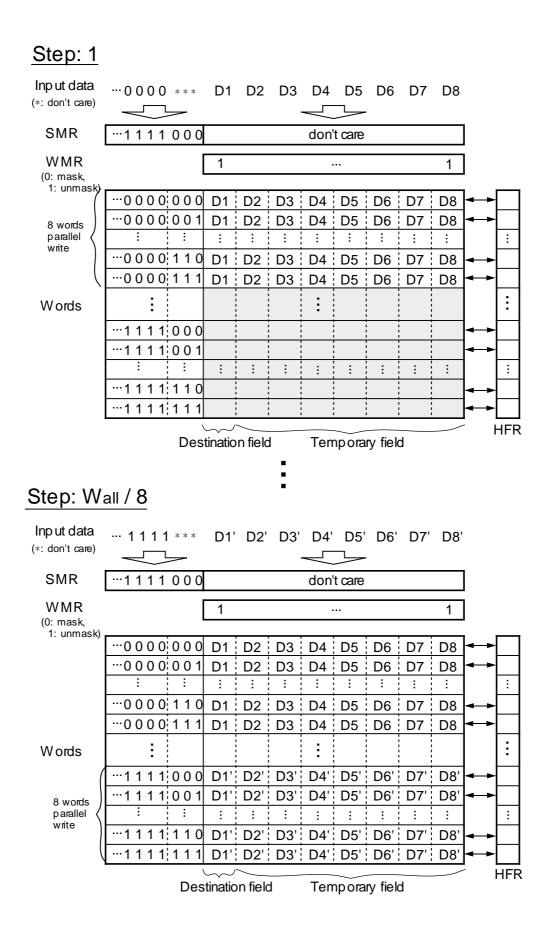

| 2.9  | Example of block data parallel write                                        | 34 |

| 2.10 | Example of inter-field transfer                                             | 35 |

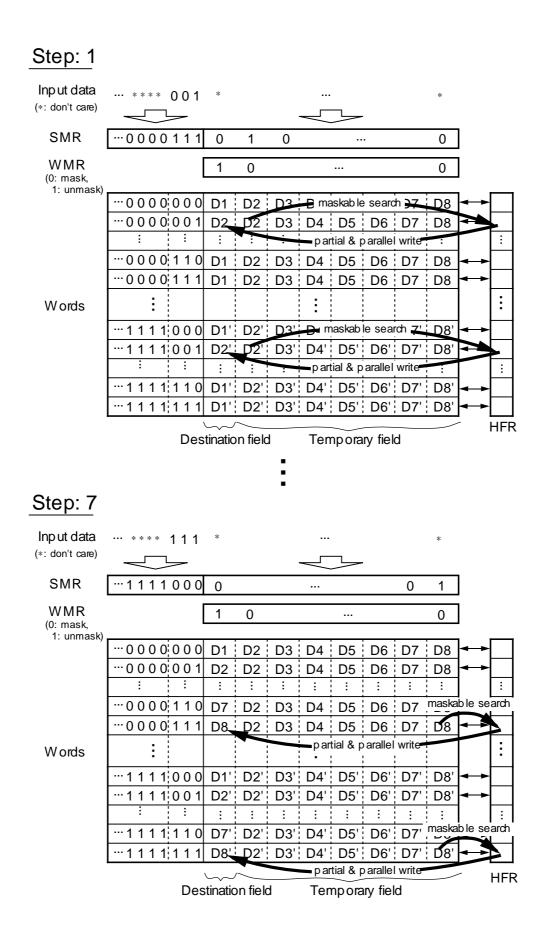

| 2.11 | Example of inter-word transfer                                              | 37 |

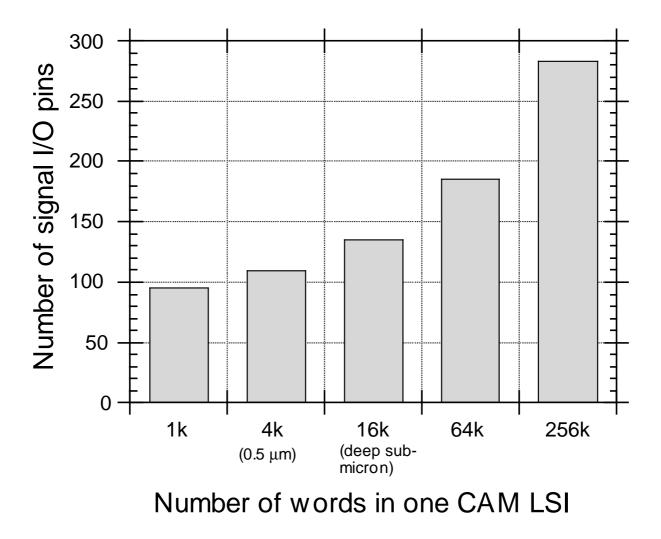

| 2.12 | Number of signal I/O pins                                                   | 39 |

| 2.13 | CA processing performance                                                   | 41 |

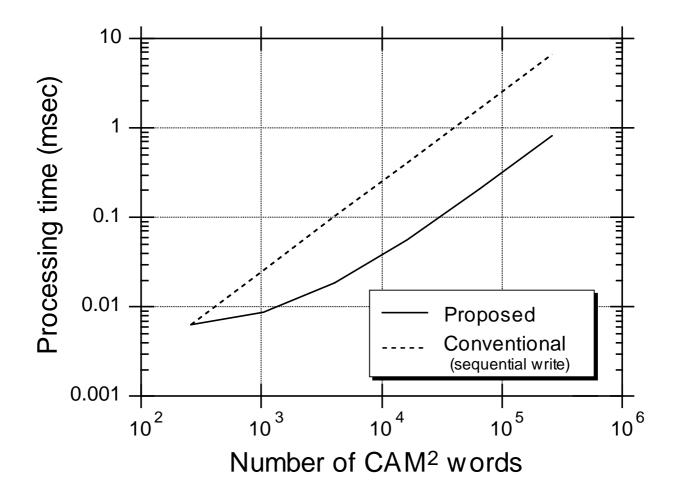

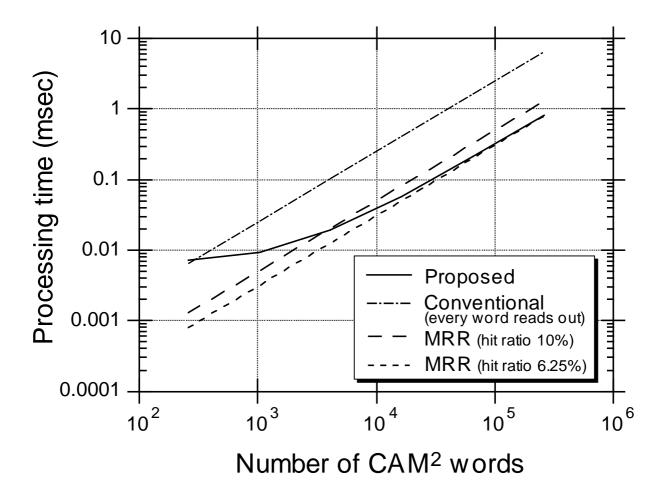

| 2.14 | Data loading performance                                                    | 43 |

| 2.15 | Data retrieving performance                                                 | 44 |

| 3.1  | Block diagram of the 1-Mb CAM                                                             | 50  |

|------|-------------------------------------------------------------------------------------------|-----|

| 3.2  | Logical configuration (multiple zigzag mapping)                                           | 52  |

| 3.3  | CAM block and cell circuits                                                               | 53  |

| 3.4  | Data and clock distribution scheme                                                        | 55  |

| 3.5  | Data transfer method.                                                                     | 57  |

| 3.6  | Area calculation. Area of (a) each CAM block and (b) whole image                          | 60  |

| 3.7  | Design and verification flow                                                              | 62  |

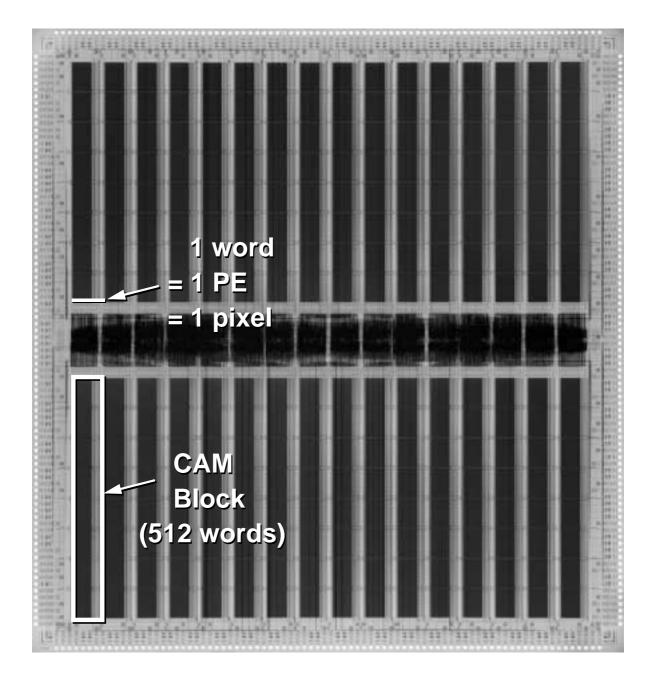

| 3.8  | Chip microphotograph                                                                      | 64  |

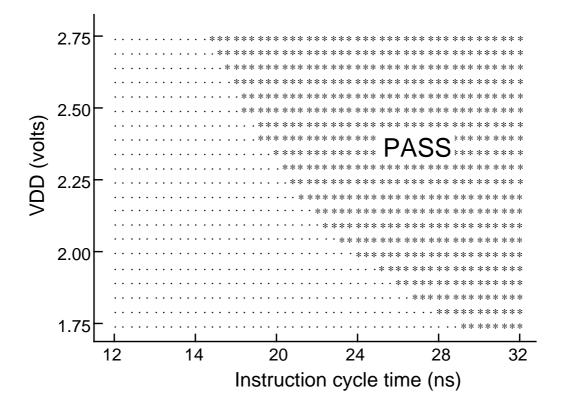

| 3.9  | Shmoo plot                                                                                | 65  |

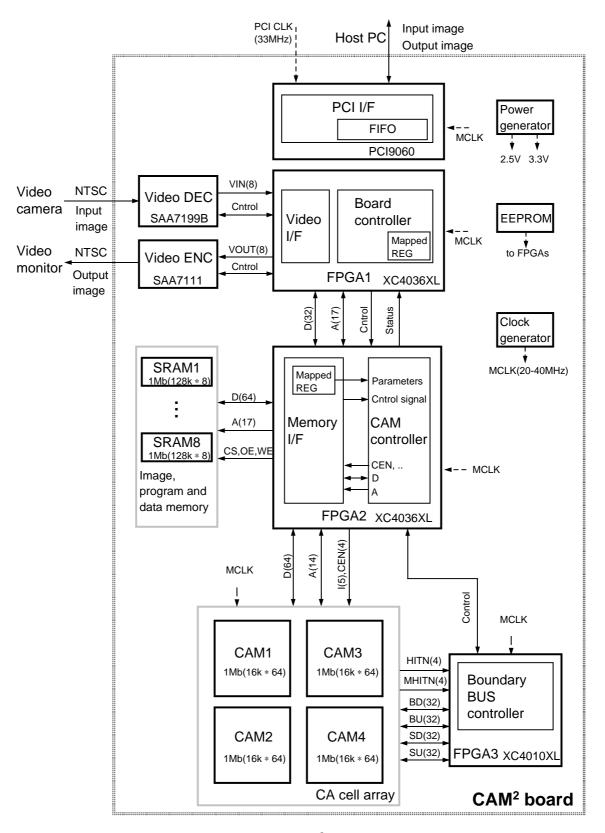

| 3.10 | Block diagram of $CAM^2$ board with four CAM LSIs                                         | 67  |

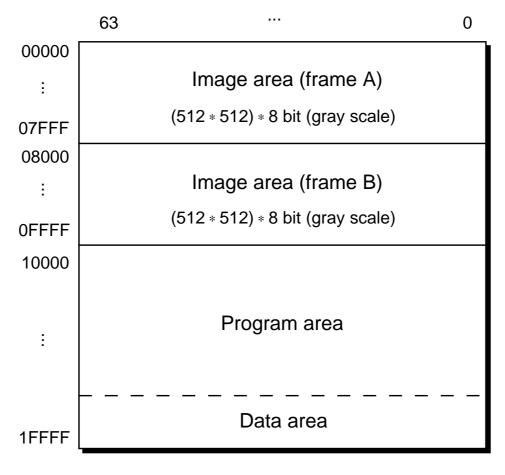

| 3.11 | Memory address map of on-board SRAM                                                       | 69  |

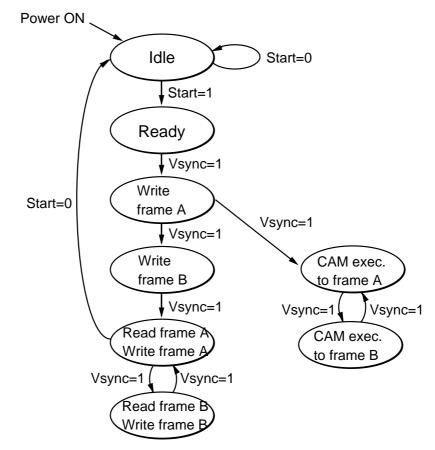

| 3.12 | Control signal flow graph and timing chart of the board controller                        | 71  |

| 3.13 | Prototype $CAM^2$ board with 256 $\times$ 256 CA cells                                    | 73  |

| 4.1  | Network structure of DTCNN                                                                | 78  |

| 4.2  | Example of CA-value $(y)$ transfer                                                        | 80  |

| 4.3  | Example of maskable search for addition                                                   | 83  |

| 4.4  | DTCNN template for hole filling.                                                          | 84  |

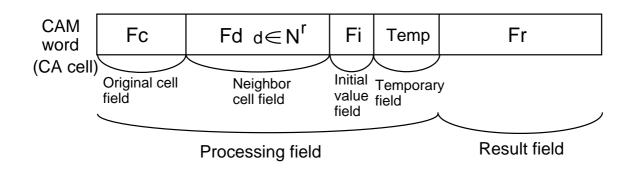

| 4.5  | CAM word configuration for DTCNN processing.                                              | 85  |

| 4.6  | Various modes of multiple-layer DTCNN                                                     | 87  |

| 4.7  | CAM word configuration for parallel mode                                                  | 87  |

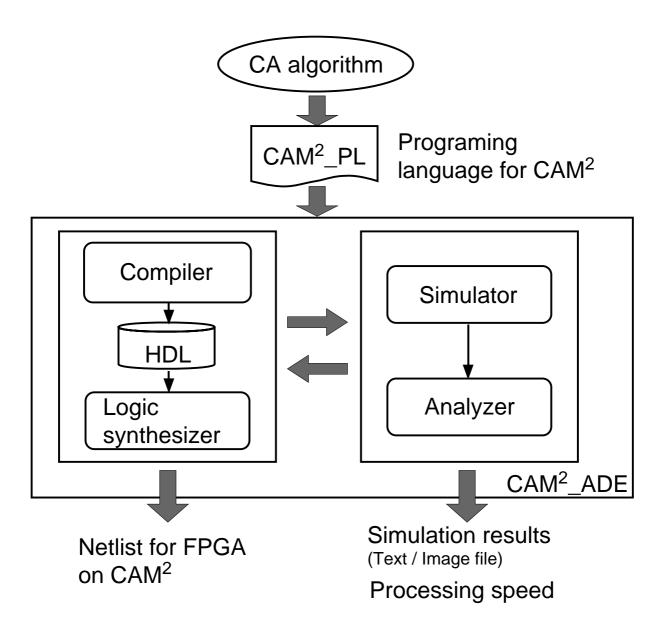

| 4.8  | Feature of $CAM^2\_ADE$                                                                   | 89  |

| 4.9  | $CAM^2\_PL$ example for hole filling                                                      | 90  |

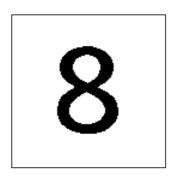

| 4.10 | Hole filling (8). $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 92  |

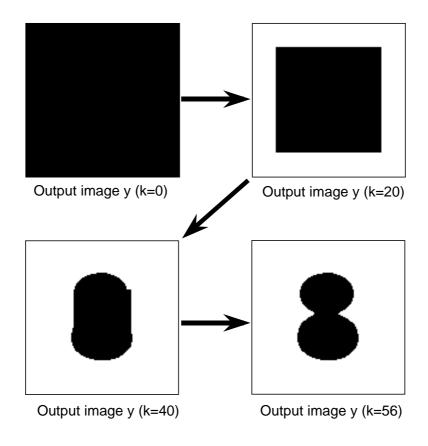

| 4.11 | Hole filling (8 with parentheses)                                                         | 93  |

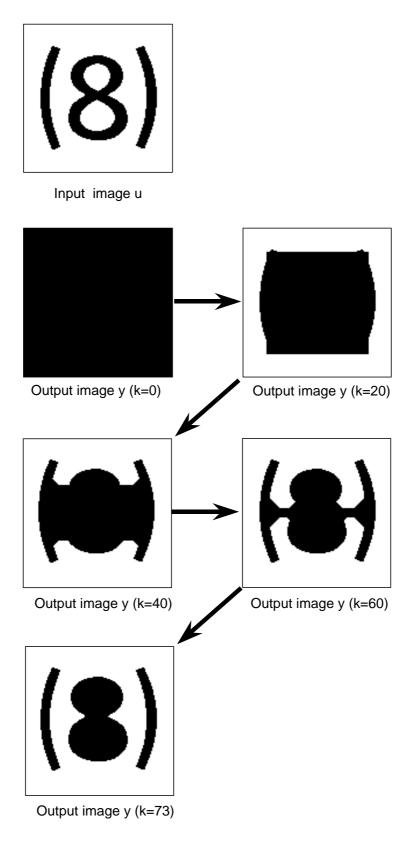

| 4.12 | Image processing based on multiple-layer DTCNN                                            | 95  |

| 5.1  | Examples of opening and closing (SP).                                                     | 104 |

| 5.2  | Example of dilation (FSP)                                                                 | 106 |

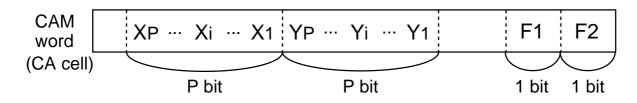

| 5.3  | CAM word configuration for dilation/erosion (rhombus)                      |

|------|----------------------------------------------------------------------------|

| 5.4  | CAM word configuration for $P$ bit less than operation                     |

| 5.5  | CAM word configuration for large and complex SEs                           |

| 5.6  | Example of pattern spectrum processing                                     |

| 5.7  | CAM structure for area calculation                                         |

| 5.8  | Basic structuring elements                                                 |

| 5.9  | Processing time for large SEs                                              |

| 5.10 | Pattern spectrum for images with and without crack                         |

| 5.11 | Morphological skeleton with various structuring elements                   |

| 5.12 | Character extraction for a license plate image with a strong shadow 122    |

| 5.13 | Multiple object tracking (morphology)                                      |

| 5.14 | $CAM^2_PL$ example for multiple object tracking                            |

| 5.15 | Multiple object tracking (other CA)                                        |

| 6.1  | Concept of a humanoid computer with multi-modal man-machine $\rm I/F.$ 133 |

# List of Tables

| 2.1 | Possible $CAM^2$ in a single PC board      | 38  |

|-----|--------------------------------------------|-----|

| 3.1 | Instruction set of CAM LSI.                | 61  |

| 3.2 | Specification of CAM LSI.                  | 65  |

| 3.3 | Processing performance at 40 MHz           | 66  |

| 4.1 | Processing time for one transition         | 91  |

| 5.1 | Processing time for basic SEs ( $\mu$ sec) | 114 |

| 5.2 | Pattern spectrum processing time           | 119 |

## Chapter 1

## Introduction

#### **1.1** Background and purpose of this dissertation

# 1.1.1 Cellular automaton as a computation paradigm for image processing

Von Neumann made two significant contributions to the history of digital computers. One was single central processing unit (CPU) computer architecture, which is generally called the von Neumann architecture. It is regarded as the most fundamental technology for creating stored-program sequential computers and is widely used to date. The other was his work in parallel computing via his research on arrays of computers. This array is called a cellular automaton (CA) [1], [2], and was originally conceived by von Neumann more than a half a century ago.

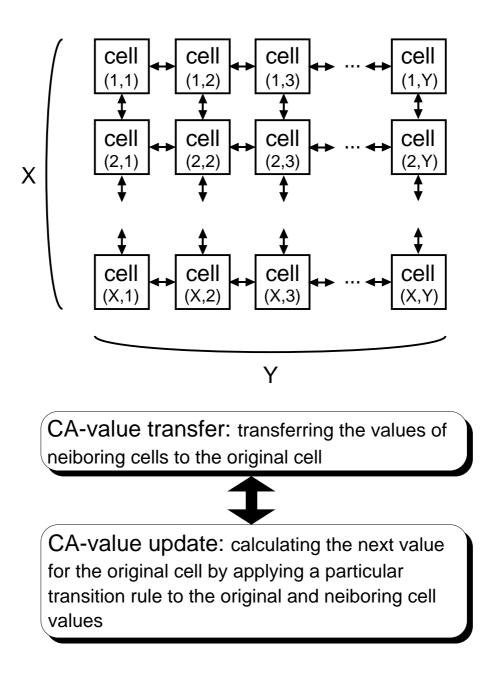

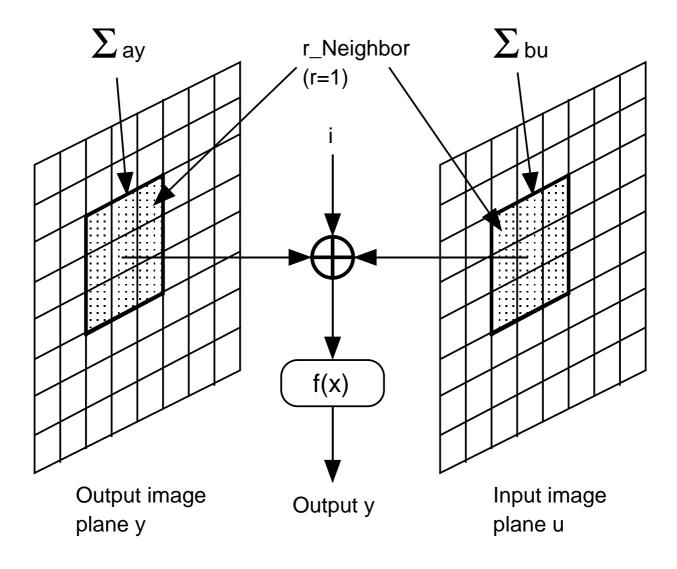

A CA is a dynamical system in which space and time are discrete. The CA consists of an array of identical computers or processing elements (PE) each with its own value and connected to its immediate neighbors. Figure 1.1 shows an example of a two-dimensional CA. CA processing is carried out by the iterative operations of CA-value transfer and update. A transfer operation involves transferring the values of neighboring cells to the original cell. An update involves calculating the next value for the original cell simultaneously in discrete steps by applying a local, identical interaction rule to the original and neighboring cell values. From the point of view of parallel machines, a CA exhibits three notable features: large-scale parallelism, local cellular interactions and simple basic components (cells). It can also be classified as a typical single instruction multiple data stream (SIMD) model based on Flynn's taxonomy [3], [4] of parallel computers. Moreover, from the programming point of view, a CA offers an extremely simple environment, compared with other parallel processing models. Even though the mechanism is very simple, a CA is a promising computer paradigm that can break through the von Neumann bottleneck that greatly degrades the performance of high performance computers required to handle large volumes of data.

Figure 1.1: Model of two-dimensional cellular automaton.

Neumann's first objective with the CA was to find a precise way of dealing with the problem of how to have machines reproduce themselves [2]. The CA was considered to provide a formal framework for investigating the behavior of complex, extended systems. Various kinds of artificial life research have been undertaken based on this concept [5]. However, the CA offers far more possibility than those for which it was first intended; it is also a promising computation paradigm for other fields. In particular, a two-dimensional CA has many applications as regards pixel-parallel image processing and low (processing from image to image) to intermediate (processing from image to symbol) level vision processing [6], because an image has a two-dimensional topology. Indeed, most conventional pixel-parallel image processing algorithms, such as segmentation, skeletonization [2] and linear filtering [7], [8], can be easily mapped on a CA. Two rather advanced applications are discrete-time cellular neural networks (DTCNN) [9], [10] and mathematical morphology [11], [12].

In spite of its great potential and long history, a CA is not widely used in the field of image-understanding processing, probably because there are no compact, practical computers that can process real-world images of several hundred thousand pixels at video rates.

#### 1.1.2 Architecture for 2D cellular automata

Vision plays an important role in the exchange of various kinds of information or even emotions in a wide range of human communication situations. Vison is also useful for obtaining various kinds of information from the real world. Thus, it is easy to believe that a vision system would have many applications both as a communicating medium and a rich sensor. Indeed, image-understanding processing is becoming indispensable for the implementation of various applications in the fields of industrial inspection, medical imaging, intelligent transportation systems (ITS), robotics, multimedia, human interface, entertainment, and image coding [8].

There are three factors that must be considered for a vision system designed to cover

this wide range of applications. The first factor is processing performance. Pixel parallel image processing and low to intermediate vision processing are indispensable for the above applications. However, this type of processing requires us to execute a very large number of logical and arithmetical operations for high-volume image data, especially for realtime applications, because it requires iterative update and data transfer operations for all pixel data. For example, performing a single operation on each pixel translates to 23 million instructions per second for a  $512 \times 512$  pixel color image. In many cases, such operations must be repeated a large number of time and many vision researchers believe that one hundred thousand times the above number of operations is required [13]. It is almost impossible for general-purpose microprocessors to handle such processing no matter how fast they might become with the progress of LSI technology. Therefore, hardware with extremely high levels of performance and high-frequency memory access is highly desirable.

The second factor is system size. Since in most vision applications, a vision system is placed in front of a user (e.g. a PC or an information terminal for human interface applications) or is embedded in some kind of on-site box (e.g. a sensor box in ITS applications), the system should be compact; otherwise, it would not be practical to use it outside a laboratory.

The last factor is flexibility. Most vision algorithms consist of various kinds of operations and their combinations. Moreover, since the computer vision field is still a rapidly evolving area of research, new algorithms are constantly being developed and tested. Innovative algorithms may continue to appear. Thus, to cover this widering range of applications, the vision system should be as flexible as possible. This means that high levels of performance, compactness and flexiblity are key factors when designing a twodimensional CA for image understanding.

Next, I survey conventional CA architectures for image processing and discuss their problems in terms of the above key factors. Conventional architecture falls into two categories: 2D SIMD cellular array and multiple-stage pipeline architecture.

#### 2D SIMD cellular array architecture

A fully-parallel two-dimensional SIMD cellular array architecture has been proposed with a view to realizing a computer for CA, or a cellular logic computer (CLC) [14]. Many machines such as CLIP-4 [15], MPP [16], AAP-2 [17], CM-2 [18] and MP-1 [19] have been developed. The fully-parallel type, which consists of two-dimensional processing elements (PEs) and interconnection networks, is the most natural architecture for twodimensional CA. The drawback of the conventional fully-parallel approach is the huge amount of hardware it requires. At most, only several dozen PEs can be embedded in one VLSI chip. Therefore, enormous numbers of VLSI chips are required if we wish to realize pixel-order (several hundred thousand) parallelism, which is crucial as regards CA performance. Moreover, two-dimensional interconnection networks cause I/O bottlenecks, so it is difficult to increase the number of PEs even if we adopt state-of-the-art LSI technology.

#### Multiple-stage pipeline architecture

Multiple-stage pipeline architectures, such as Cytocomputer [20] and CAM8 [21] have also been proposed for CLC. Since these machines are not true CA, they are also called cellular automaton machines. This architecture can achieve high-performance CA processing, but the hardware structure must be fully tuned to the application because the most suitable configuration is different for different applications. Due to this lack of flexibility, it is not truly suitable for practical pixel-level image processing that requires various CA processes.

Against this backdrop, it is very clear that conventional architectures are unsatisfactory solutions to the problem of developing compact, practical, and flexible CA for image-understanding processing. The purpose of this study is to develop a compact, high-performance, flexible highly-parallel two-dimensional cellular automaton for realtime image-understanding processing. The result is CAM<sup>2</sup>, which stands for Cellular AutoMata on Content-Addressable Memory.

#### 1.2 Key technologies: HiPIC and CAM

I focused on two important technical isues with a view to achieving the goal of my research, namely the development of a compact, high-performance, and flexible CA called CAM<sup>2</sup>. These issues were the system model and the LSI architecture. The former is the key to creating a flexible system. The latter is the key to achieving both high levels of performance and compactness simultaneously.

#### **1.2.1** System model for image processing

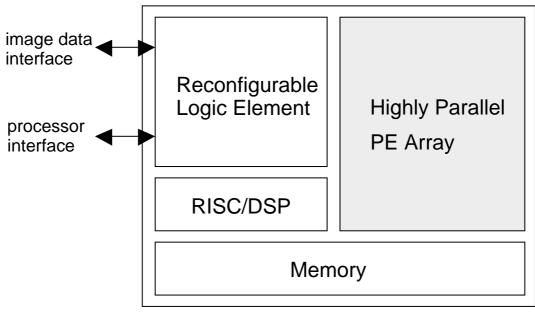

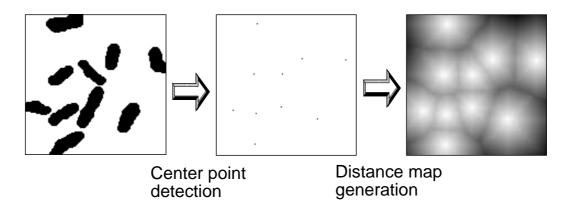

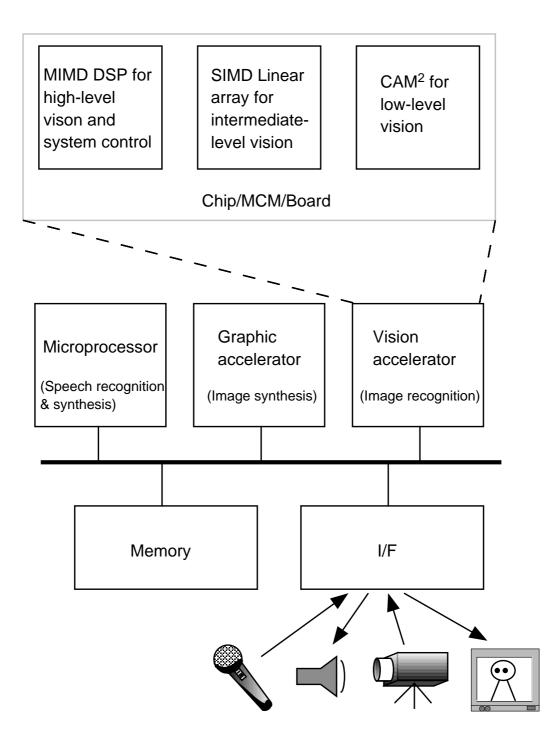

The highly-parallel integrated circuits and system (HiPIC) concept is used as the system model for real-time image processing. HiPIC is a highly-parallel system model devised for application-specific systems, to achieve both high levels of performance and flexibility. Figure 1.2 shows the basic idea of HiPIC. A HiPIC consists of a highly-parallel PE array, a reconfigurable logic element, a reduced instruction set computer (RISC) processor or a digital signal processor (DSP), and some memory. It can be implemented on a chip, as a multi-chip module, or on a board. The highly-parallel PE array (shaded block in the figure) performs SIMD processing for high-volume image data. The logic element controls the PE array and interfaces with the image data and an external processor. The processor performs serial data processing.

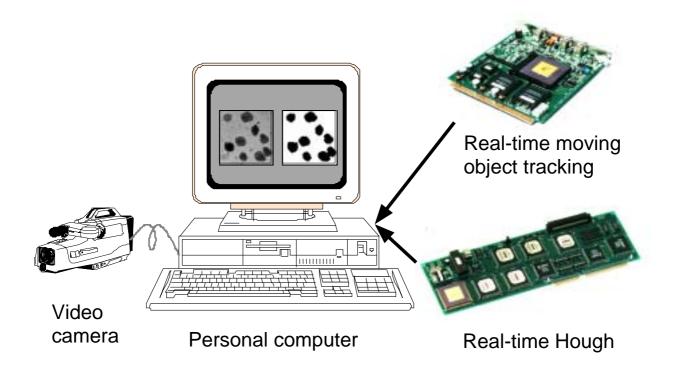

Various practical real-time image processing systems and their hardware algorithms, such as the facial image tracking (FIT) system [23] and the voting system [24] – [28], have already been developed based on HiPIC. Figure 1.3 shows examples of HiPIC systems. The board in the upper right of the figure is used for the real-time tracking of moving objects utilizing CAM-based local spiral labeling [23]. Labeling is one method of basic image processing, and it involves applying a unique label number to each closed region in the image. The board in the lower right of the figure is for shape and feature extraction based on the CAM-based Hough transform, and 3D projection, which are both voting methods. It can perform line and circle detection [24] – [27] and 3D feature extraction [28]. They are implemented as add-on boards for personal computers, which makes them

Chip/MCM/Board

Figure 1.2: Basic idea of HiPIC.

Figure 1.3: Image processing systems on HiPIC.

easy to use. These systems demonstrate that HiPIC is a very effective way to handle real-time image processing, which is why I also employed it as a system model for CAM<sup>2</sup>.

#### **1.2.2 LSI architecture for CA cell array**

The other issue is the LSI architecture for a CA cell array. The performance of  $CAM^2$  depends strongly on the data processing capabilities of the PE or CA cell array. The most important thing is that the array must have sufficient parallelism implemented in very little hardware. For example, several hundred thousand PEs are required for practical image processing. That means that the PE has to be simple. In addition, to avoid the von Neumann bottleneck, the most suitable PE is the logic-in-memory type. Based on these considerations, I can think of a CAM turned to CA processing as a PE array of CAM<sup>2</sup> on HiPIC.

Next, I survey related LSI architectures targeted for image processing. Then, I address the features and problems of conventional CAMs by comparison with these architectures.

#### Media processor chip

One promising LSI for creating a compact high-performance image-understanding system is a media processor [29], [30] or a microprocessor with multimedia extensions (MMX) [31], [32] which has dedicated parallel operations for image processing. This LSI is based on microprocessor technologies, and it is easy to make a high-frequency chip. However, the degree of parallelism is not very high. This prevents the full use of the abundant parallelism of pixel-parallel algorithms; and, as a result, the processing speed is insufficiently high many real-time applications.

#### Linear array processor chip

The degree of parallelism of a linear array processor [33], [34] is relatively high because of its simple and regular structure. However, since it can only perform one-dimensional processing (line data can be handled in parallel), iterative operations (in proportion to image size) are required to develop an entire image. By adopting a higher-performance processing element (PE) like IMAP [33] with 8-bit-width PEs, the processing performance can be boosted. However, since the bit width of each PE is fixed, it is less flexible as regards the bit width of processed data. For example, its processing power cannot be fully utilized for a binary image.

#### Analog vision chip

An analog vision chip [35] - [37], which features imaging devices, such as photo detectors, and computational circuits on a single chip, is another candidate. However, it is extremely difficult to develop a large-capacity chip that can process a practical image of several hundred thousand pixels because of problems with reliability, accuracy, and production yield. Therefore, most vision processors contain very few elements, and since they do not have scalability, even if plural chips are used, they cannot handle a larger (realworld) image. Furthermore, since each element has extremely limited functions, there is insufficient flexibility for practical, or complex, image processing.

#### Content addressable memory (CAM)

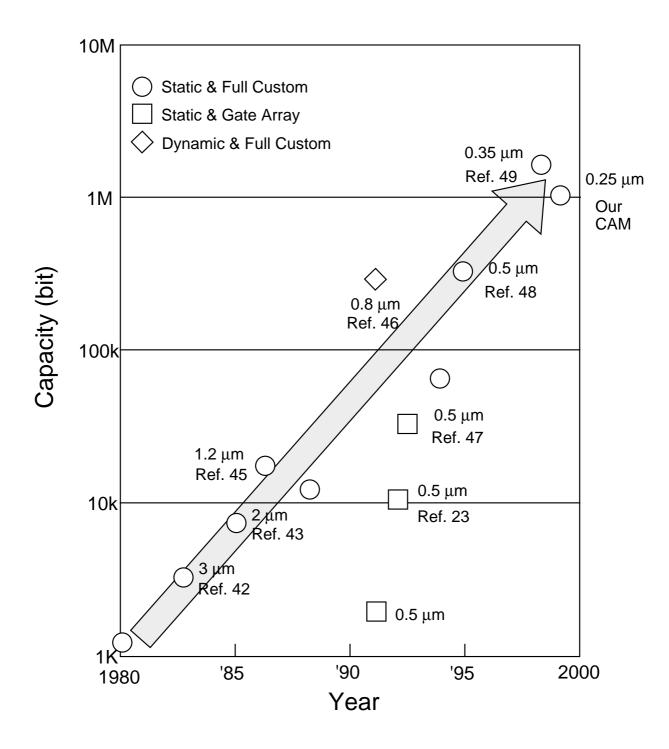

Content addressable memory (CAM) is well known as a functional memory [38] – [41] and various types of CAM [42] – [49] have been developed since about 1980. The development trends for fully-parallel CAMs, excluding ROM and EEPROM types, are shown in Fig. 1.4.

The CAM capacity is proportional to the progress of LSI technology because CAM's memory-based structure is the most suitable for implementation with LSI technology. Indeed, as shown in Fig. 1.4, CAM capacity is increasing almost exponentially and this trend will last until the current progress on LSI process technology saturates. Moreover, its high-density structure enables us to reduce the wiring capacitance, which is the main factor behind rising power consumption. Therefore, a high capacity LSI can be implemented without causing a power consumption bottleneck.

Conventional CAMs fall into two categories:

1. CAM with only a search function, and

Figure 1.4: CAM development trend.

2. CAM with a parallel write function in addition to a search function.

Although the former type, which accounts for most of the conventional CAMs, has a particularly high capacity (e.g. the 2.5 Mb CAM [49]), it has only been used as a search engine in a LAN or for similar applications because of its limited functionality. In contrast, the latter type of CAM, which is also called an associative processor or a content addressable parallel processor [50], is capable of not only a parallel search but also various types of parallel data processing with words as the basic unit. This makes it a promising candidate for creating a compact, highly-parallel image processing system that requires both high levels of performance and high data throughput.

One example of an associative processor for image processing is the content addressable array parallel processor (CAAPP) [51]. It incorporates advanced communication networks, such as coterie networks, to allow it to perform a wider range of low-level computer vision applications. But only 256, or  $16 \times 16$ , PEs are embedded in one VLSI chip. Therefore, enormous numbers of chips are required to realize pixel-order parallelism. Moreover, since its network structure becomes extremely complicated as the array size is increased, it is difficult to increase the number of PEs even if we use state-of-the-art LSI technology. The 336 k-bit CAM [48] and the pixel-parallel image processor [52] are examples with a relatively large number of PEs (4096 PEs) reported to date. However, the 336 k-bit CAM does not have an efficient mechanism for transferring data between words, while the image processor has no functions for global data handling. This lack of flexibility severely limits their usefulness for pixel-parallel image processing applications. Moreover, they still have insufficient capacity; many chips,  $16 \times 64$ , are required to achieve pixel-order parallelism (several hundred thousand pixels).

#### 1.3 Thesis scope

The objective of this dissertation is to describe the development of a compact, highperformance, flexible highly-parallel two-dimensional cellular automaton for real-time image-understanding processing. To attain this goal, this thesis focuses on three areas of research:

- 1. computer architecture,

- 2. LSI and system design and implementation, and

- 3. applications.

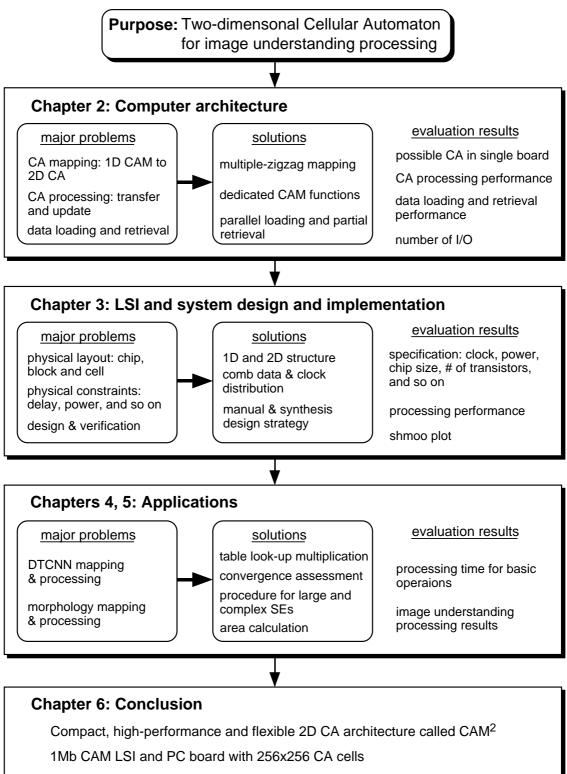

To cover these three areas, the thesis consists of six chapters as shown in Figure 1.5.

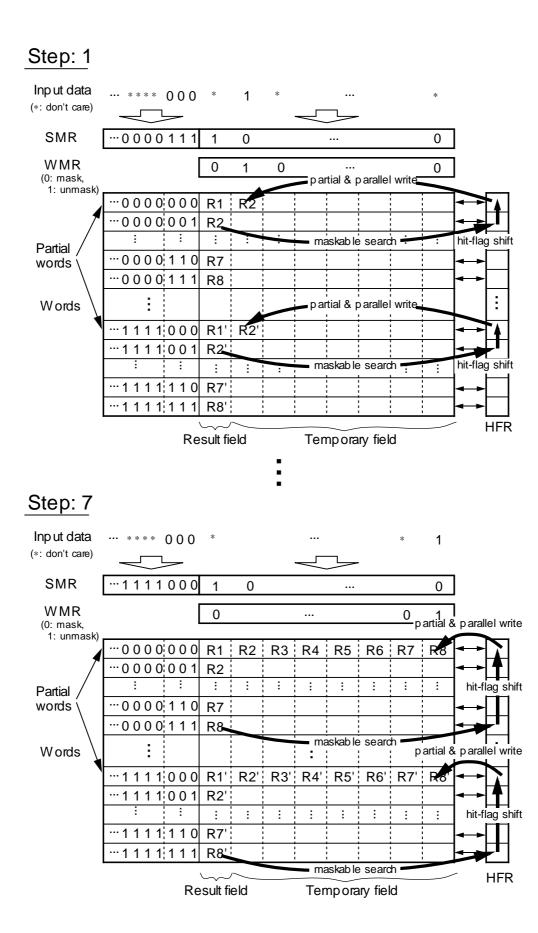

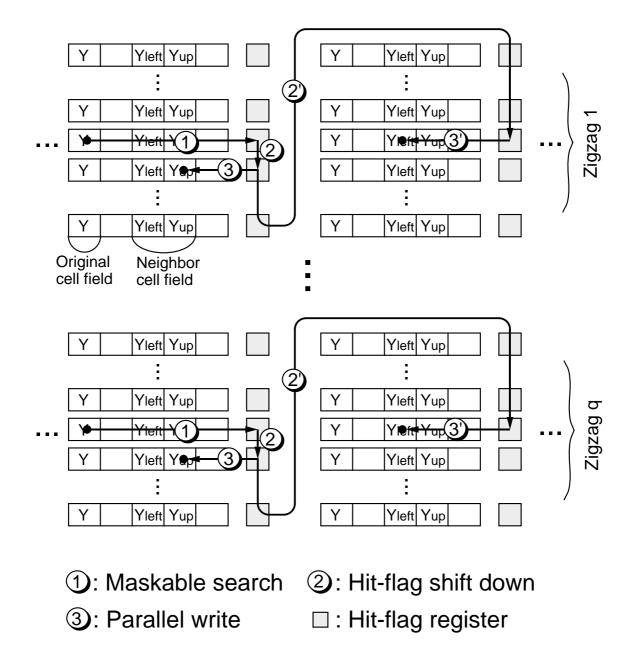

Chapter 2 describes the basic architectural concepts and technologies of a highlyparallel two-dimensional cellular automaton architecture called CAM<sup>2</sup>. CAM<sup>2</sup> is established on a system model called HiPIC and on CAM technologies. Both are vital for realizing a compact, high-performance, and flexible two-dimensional CA. The main theme of my CAM<sup>2</sup> study effort focused on the following three architectural considerations: CA mapping, CA processing, and data loading and retrieval processing. Multiple-zigzag mapping enables two-dimensional CA cells to be mapped into CAM words, even though physically a CAM has a one-dimensional structure. Dedicated CAM functions, such as the shift up/down mode for hit flag, enable high-performance CA processing. Furthermore, parallel loading and partial word retrieval techniques enable high throughput data transfer between CAM<sup>2</sup> and the outside image buffer. Chapter 2 also presents various results of a performance evaluation based on CAM<sup>2</sup>, such as possible CAM<sup>2</sup> in a single PC board, and CA processing and data loading and retrieval processing performance.

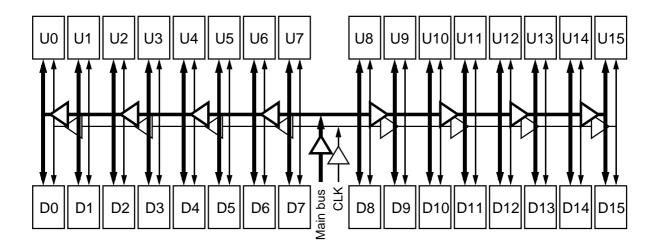

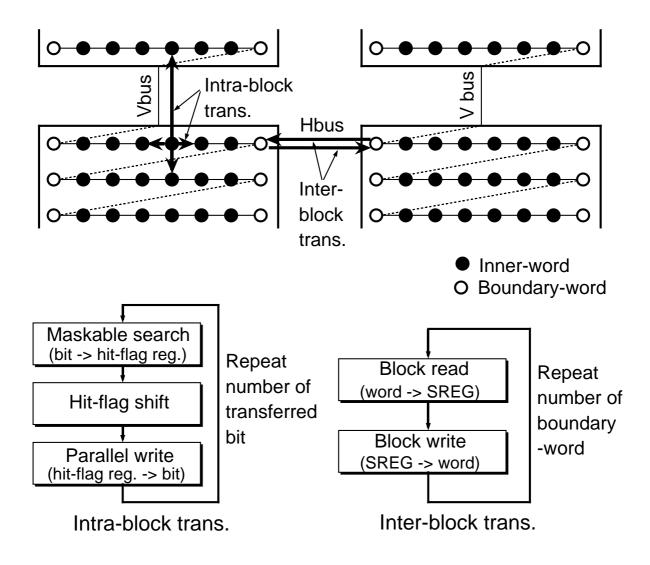

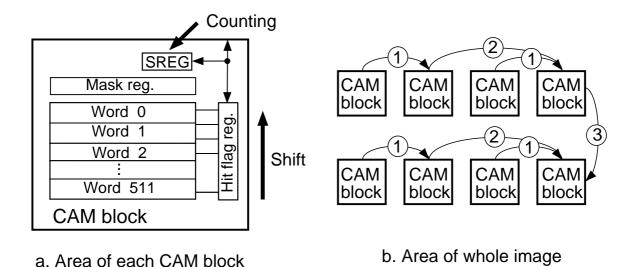

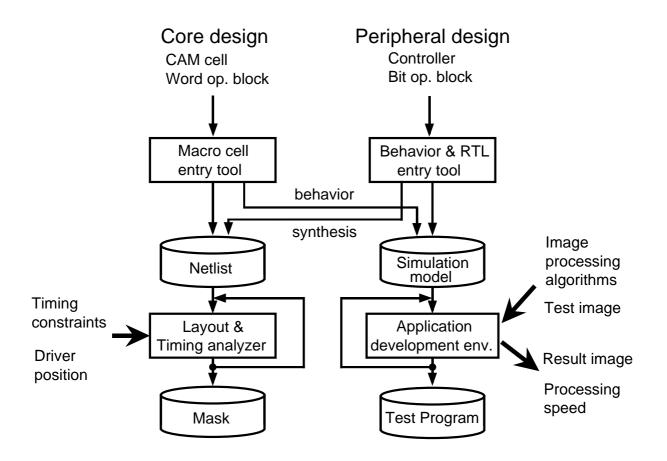

Chapter 3 describes a fully-parallel 0.25  $\mu$ m 1-Mb CAM LSI with dedicated functions for CA processing and a prototype CAM<sup>2</sup> PC board using this CAM chip. To make such a large capacity CAM that satisfies the extremely severe design constraints of state-of-theart process technology (0.25  $\mu$ m), this study involves not only VLSI circuit design, but also packaging technology, circuit board fabrication technology, power and signal distribution techniques, heat dissipation problems and design and verification strategy. Concretely, I devise a scheme that combines one-dimensional (intra-block) and two-dimensional (interblock) physical structures and comb data and clock distribution techniques. Moreover, I propose both manual and synthetic design strategies to speed up chip development while achieving a CAM with a high-density structure. Chapter 3 also presents various estimation results, related to such factors as operating frequency, power consumption and chip size, based on an actual fabricated chip.

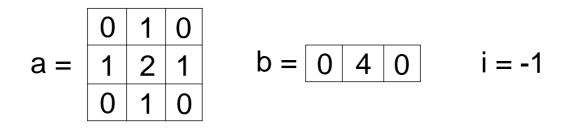

Chapters 4 and 5 describe image processing applications of  $CAM^2$  to demonstrate that CAM<sup>2</sup> has wide applicability to various kinds of practical real-time image processing. Many basic image processing algorithms based on CA, such as segmentation, skeletonization and cellular filtering, have already been proposed [2] and it is clear that  $\mathsf{CAM}^2$  can also handle them efficiently. Here, I focus on two advanced computation paradigms based on CA. These two paradigms are discrete-time cellular neural networks (DTCNN) [9], [10] and mathematical morphology [11], [12]. DTCNN is a promising computer paradigm that fuses artificial neural networks with cellular automaton (CA) concept. Mathematical morphology is an image transformation technique that locally modifies geometric features through set operations. Both are powerful tools with various applications in the field of image processing where they are becoming very commonly used [53], [54]. Here, I study a mapping and processing method designed to perform various kinds of DTCNN and morphology processing. New mapping and processing methods achieve high-throughput complex DTCNN and morphology processing. Chapters 4 and 5 also present processing time estimation results and various kinds of image processing. CAM<sup>2</sup> performs practical image processing, such as pattern spectrum and multiple object tracking, through a combination of DTCNN and morphology and other algorithms.

Chapter 6 summarizes the results of these research activities from the standpoint of computer architecture, LSI and system implementation and applications. Chapter 6 also indicates the future direction of research that will further improve the performance of  $CAM^2$  and expand its use to various kinds of vision application.

Real-time image understanding processing based on DTCNN and morphology

Figure 1.5: Organization of this dissertation.

## Chapter 2

# Cellular automaton architecture: $\mathbf{CAM}^2$

#### 2.1 Introduction

In this chapter, I explain a highly-parallel two-dimensional cellular automaton architecture called CAM<sup>2</sup> in detail from an architectural point of view. CAM<sup>2</sup> can attain pixel-order parallelism on a single PC board because it is composed of a CAM, which makes it possible to embed an enormous number PEs, corresponding to CA cells, onto one VLSI chip.

The major research subject that must be studied is mapping method of two-dimensional CA into a CAM. I devised multiple-zigzag mapping and horizontal and vertical inter-CAM connection networks for it. They enable two-dimensional CA cells to be mapped into CAM words, even though physically a CAM has a one-dimensional structure. Another important subject is how to execute CA processing on a CAM. Since conventional CAM cannot perform it, I devised dedicated CAM functions, such as the shift up/down mode for hit flag. These functions are carefully chosen not to lose CAM's simplicity, which is the most important factor to create a high-density CAM. I also propose Intra- and inter-CAM transfer procedures for CA-value transfer. These functions and procedures enable high-performance CA processing. Data loading and retrieval processing, which are rather common problems for most parallel processors, is also an important subject to study. I propose parallel loading and partial word retrieval techniques that are fully utilized CAM's feature to solve this problem. They enable high throughput data transfer

between  $\mathsf{CAM}^2$  and the outside image buffer.

I also show various results of a performance evaluation based on CAM<sup>2</sup> in this chapter. Possible CAM<sup>2</sup>, such as CA cell size and number of I/O pins, in a single PC board is estimated based on the trend of state-of-the-art VLSI and CAM technologies. Furthermore, I present results of CA processing and data loading and retrieval processing performance. For the evaluation, the functional hardware model of CAM<sup>2</sup> written in Verilog-HDL [55] was developed.

This chapter is organized as follows. Section 2.2 presents the basic architecture of CAM<sup>2</sup>. This is followed, in Section 2.3, by a description of the CA processing. After discussing the data loading and retrieval techniques in Section 2.4, the performance evaluation results are shown in Section 2.5.

#### 2.2 Basic architecture

As described in Chapter 1, CAM<sup>2</sup> is established on a system model called HiPIC (highlyparallel integrated circuits and system) and on CAM technologies [22], [45]. Both are vital for realizing the compact, high-performance, and flexible two-dimensional CA. First of all, I explain how these technologies apply for creating CAM<sup>2</sup>.

### 2.2.1 CAM<sup>2</sup> based on HiPIC

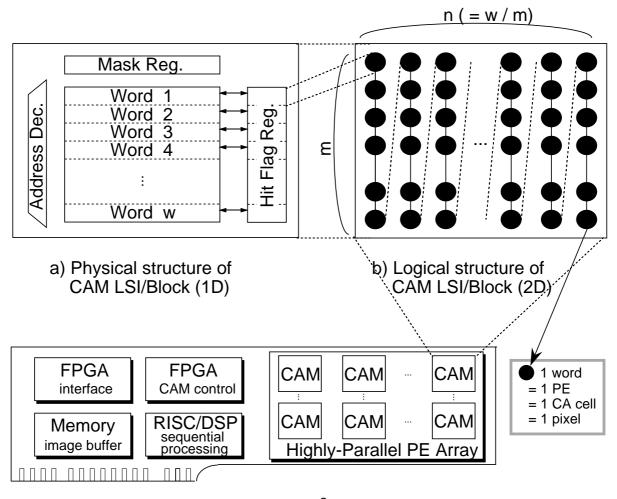

Figure 2.1 shows features of  $CAM^2$  on HiPIC.

c) Structure of CAM<sup>2</sup> board

Figure 2.1: Features of  $CAM^2$  on HiPIC.

According to the HiPIC concept, CAM<sup>2</sup> consists of a highly-parallel PE array, a field programmable gate array (FPGA), a RISC processor or DSP, and some memory. The PE array, which is the most important component in CAM<sup>2</sup>, is a two-dimensional array of the proposed CAMs. Its main features are CAMs with dedicated functions for CA processing and multiple-zigzag mapping. The dedicated CAM functions enable high-performance CA processing, while the multiple-zigzag mapping enables two-dimensional CA cells to be mapped into CAM words, even though physically a CAM has a one-dimensional structure as shown in Fig. 2.1. The dedicated CAM and the PE array with multiple-zigzag mapping will be explained in detail in Sections 2.2.2 and 2.2.3, respectively. The FPGA controls the highly-parallel PE array. The control logic, which generates command sequences for CA processing, is mapped into the FPGA. Since an FPGA can easily rewrite the logic, CAM<sup>2</sup> performs various types of CA-based image processing, such as discrete-time cellular neural networks [9], [10], mathematical morphology [11], [12], linear filtering [7], either alone or in combination. (The processing methods of DTCNN and morphology will be described in detain in Chapters 4 and 5, respectively.) Furthermore, the interface logic is also mapped into the FPGA. By changing the logic, CAM<sup>2</sup> can be embedded into various computer platforms.

The processor performs serial data processing. Since it can be used for various preand post-CA processing, CAM<sup>2</sup> can handle total image processing, including higher-level processing.

The memory is used as a buffer. It stores input images, temporary data, and processed data. It is also used for storing some programs for the FPGA.

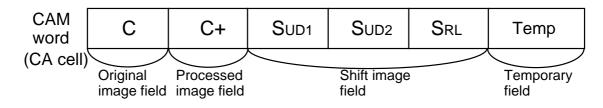

#### 2.2.2 Dedicated CAM features for CAM<sup>2</sup>

CA processing is carried out by iterative operations of CA-value transfer and update. To perform both operations effectively, the dedicated CAM for CAM<sup>2</sup> has the following functions.

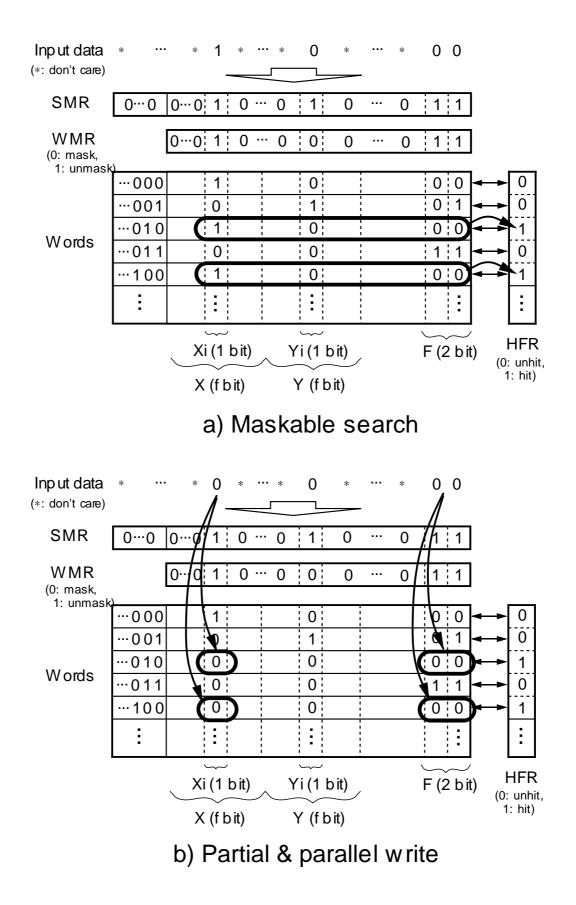

- Word read/write using addresses (2.a)

- Maskable search (2.b)

- Parallel/partial write (2.c)

- Shift up/down mode for hit flag (2.d)

- Parallel execution of hit flag shift (2.d) and word read/write (2.c) (2.e)

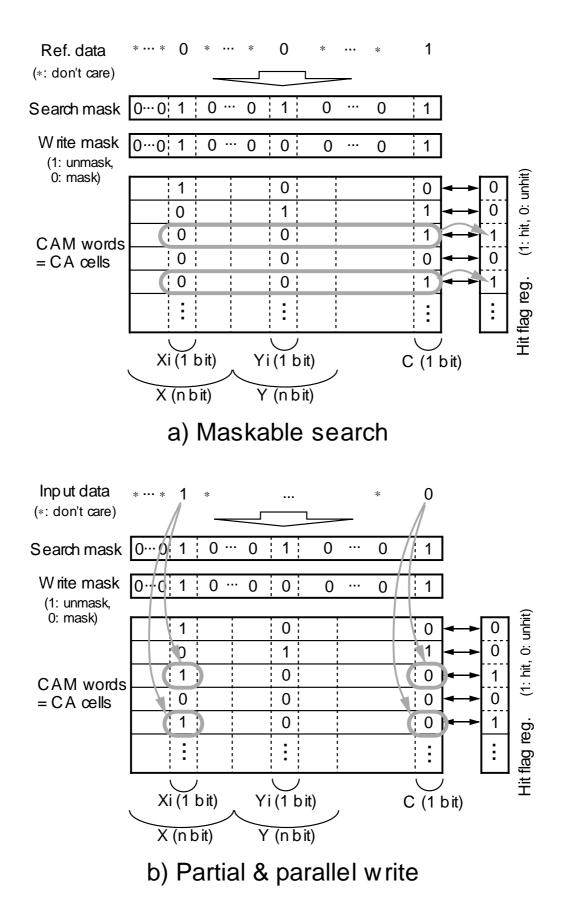

The dedicated CAM can perform normal RAM operations, such as word reads and writes using addresses (2.a). Using (2.a), every word can be directly accessed from/to Data I/O. Furthermore, it can also operate as a SIMD PE array and do such things as a

maskable search (2.b), and partial and parallel writes (2.c). For the search, the results are accumulated in hit-flag registers by means of OR logic. For the writes, the data are written into specific bit positions of multiple words for which the value of the hit-flag register is 1. Through the iteration of these two operations, the SIMD-type PE operations, such as general associative, logical and arithmetic operations, can be carried out in a bit-serial, word-parallel manner.

Our previously developed CAMs [45], [22] also have functions (2.a)-(2.c). However, the data transfer between neighboring CA cells, which is indispensable for CA processing, cannot be performed using only these functions. Therefore, two dedicated operations are added: upward and downward hit-flag shift (2.d), and the parallel execution of a hit-flag shift and a read or write using an address (2.e). These functions can be implemented just by changing the peripheral circuit of CAM, i. e., changing the memory cell part is unnecessary. So, the dedicated CAM LSI for CAM<sup>2</sup> can be easily built by making minimum refinements to our previously developed CAMs, such as the 0.5- $\mu$ m 336 k-bit CAM [48].

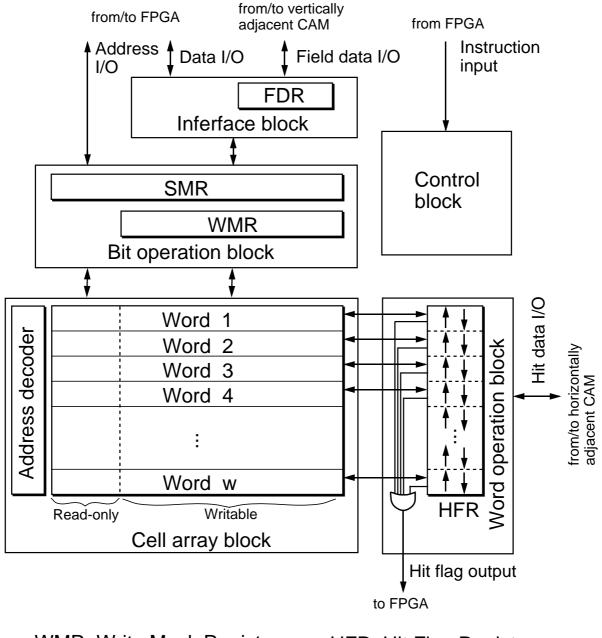

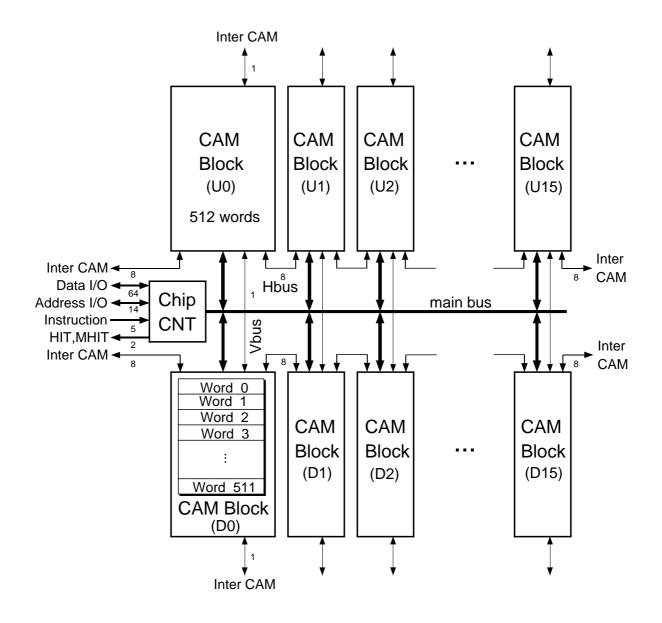

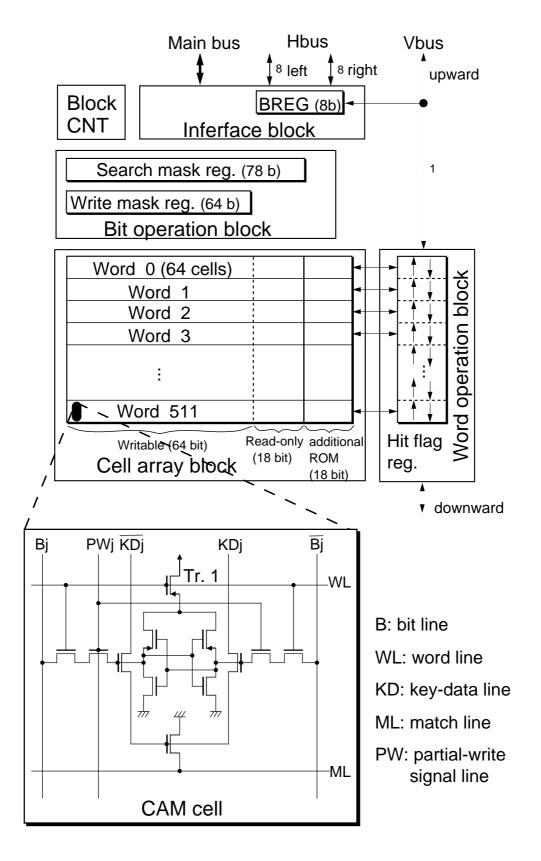

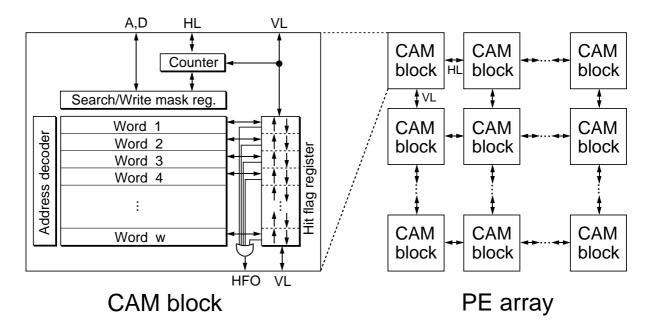

Figure 2.2 shows a block diagram of the dedicated CAM for CAM<sup>2</sup>. It consists of five function blocks: a cell array block, a bit operation block, a word operation block, an interface block and a control block.

The cell array block is composed of an address decoder and words whose number is w. The word is divided into writable bits and read-only bits. The writable bits can perform both the maskable search (2.b) and the parallel write (2.c). So, SIMD-type PE operations can be carried out to data on the bits. On the other hand, the read-only bits store fixed address data and can only perform the maskable search (2.b) for the data. By masking the read-only bits, plural words can be addressed.

The bit operation block controls the bit position for the maskable search (2.b) and the parallel write (2.c). It is composed of a search mask register (SMR) and a write mask register (WMR). SMR stores search mask data for both the writable and read-only bits. WMR stores write mask data for only the writable bits.